#### **General Description**

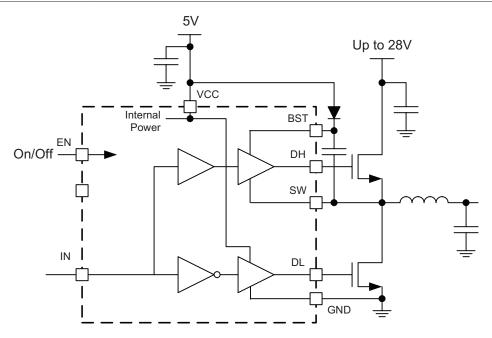

The AAT4910 is a 28V half-bridge dual MOSFET driver for high-current DC-DC converter and motor driver applications. It drives both high-side and low-side N-channel MOSFET switches controlled by a logic input. The internal driver circuitry and MOSFET driver power comes from a 5V input allowing the use of low-threshold MOSFETs. The high-side driver output stage is allowed to float at up to 28V, allowing a broad range of power sources.

The AAT4910 is available in a Pb-free, space-saving SC70JW-8 package and is rated over the -40°C to  $85^{\circ}$ C temperature range .

#### **Features**

- Input Voltage Range up to 28V

- Dual N-Channel MOSFET Switches

- Shoot-Through Protection

- Over-Temperature Protection

- Available in 2.0 x 2.2 mm SC70JW-8 Package

- -40°C to 85°C Temperature Range

### **Applications**

- · Class D Audio

- High Current Synchronous DC-DC Converter

- Motor Drivers

- Multiphase DC-DC Converters

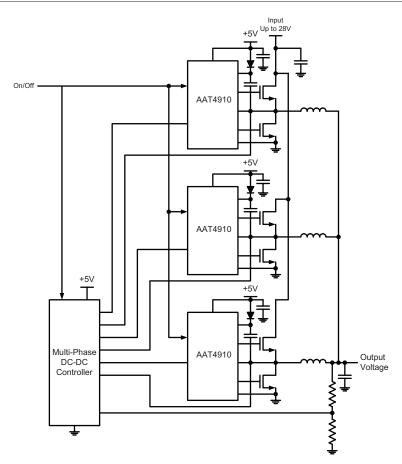

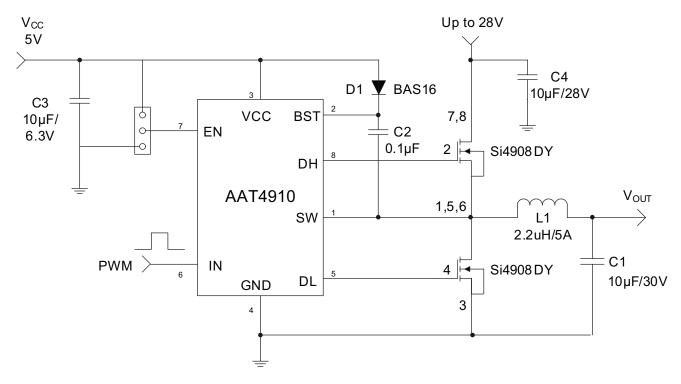

### **Typical Application**

## 28V Half-Bridge Dual N-Channel MOSFET Driver

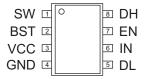

### **Pin Descriptions**

Pin numbers are preliminary and subject to change.

| Pin # | Symbol                                                                                                                                    | Function                                                                                                                                                                                                                                                                                                                      |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | SW                                                                                                                                        | Switching node. SW is the switching node. This is the return for the high-side MOSFET drive. Connect SW to the high-side MOSFET source and the low-side MOSFET drain.                                                                                                                                                         |  |

| 2     | BST                                                                                                                                       | Boosted drive input for high side gate driver. BST supplies power to the high-side MOSFET gate drive allowing the gate drive voltage higher than the input voltage for full enhancement of the high-side MFET. Connect the boost capacitor between SW and BST, and connect a diode from VCC to BST to chathe boost capacitor. |  |

| 3     | VCC                                                                                                                                       | Input supply voltage. Connect VCC to the 5V bias supply voltage. Bypass VCC to GND with a $1\mu F$ or greater capacitor as close to the AAT4910 as possible.                                                                                                                                                                  |  |

| 4     | GND                                                                                                                                       | Ground.                                                                                                                                                                                                                                                                                                                       |  |

| 5     | DL                                                                                                                                        | Low-side MOSFET gate drive output. DL drives the gate of the low-side MOSFET. Connect the gate of the low-side MOSFET to DL.                                                                                                                                                                                                  |  |

| 6     | IN                                                                                                                                        | IN Logic signal input. The state of IN determines if the high-side or low-side switch is on/off. Drive IN high to turn on the high-side switch, drive IN low to turn on the low-side switch.                                                                                                                                  |  |

| 7     | EN                                                                                                                                        | Enable input. Drive EN high to turn on the AAT4910, drive it low to turn it off. When EN is low, both DH and DL are driven low to turn off the external MOSFETs. For automatic operation, connect EN to VCC.                                                                                                                  |  |

| 8     | DH High-side MOSFET gate drive output. DH drives the gate of the high side MOSFET. Connect the gate of the high-side MOSFET switch to DH. |                                                                                                                                                                                                                                                                                                                               |  |

### **Pin Configuration**

SC70JW-8 (Top View)

## 28V Half-Bridge Dual N-Channel MOSFET Driver

### Absolute Maximum Ratings<sup>1</sup>

| Symbol | Description                                      | Value                    | Units |

|--------|--------------------------------------------------|--------------------------|-------|

|        | VCC Voltage to GND                               | -0.3 to 6.0              | V     |

|        | DL Voltage to GND                                | $-0.3$ to $V_{IN} + 0.3$ | V     |

|        | SW to GND                                        | -2 to 28                 | V     |

|        | DH Voltage to SW                                 | -0.3 to 6                | V     |

|        | DH Voltage to BST                                | +0.3 to -6               | V     |

|        | BST Voltage to SW                                | -0.3 to 6.0              | V     |

|        | IN, EN Voltage to GND                            | -0.3 to 6.0              | V     |

|        | Operating Junction Temperature Range             | -40 to 150               | °C    |

|        | Maximum Soldering Temperature (at leads, 10 sec) | 300                      | °C    |

#### **Thermal Information**

| Symbol         | Description                                                | Value | Units |

|----------------|------------------------------------------------------------|-------|-------|

| P <sub>D</sub> | Maximum Power Dissipation (SC70JW-8)                       | 625   | mW    |

| $\theta_{JA}$  | θ <sub>JA</sub> Thermal Resistance (SC70JW-8) <sup>2</sup> |       | °C/W  |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Mounted on a FR4 board.

### 28V Half-Bridge Dual N-Channel MOSFET Driver

#### **Electrical Characteristics<sup>1</sup>**

$T_A = -40$  °C to 85 °C, unless otherwise noted. Typical values are  $T_A = 25$  °C,  $V_{VCC} = V_{BST} = 5.0$ V.

| Symbol             | Description                               | Conditions                                                | Min  | Тур | Max | Units |  |

|--------------------|-------------------------------------------|-----------------------------------------------------------|------|-----|-----|-------|--|

|                    | In-Circuit Operating Input Voltage        |                                                           |      |     | 28  | V     |  |

|                    | VCC Input Voltage                         |                                                           | 4.5  |     | 5.5 |       |  |

|                    | UVLO Threshold                            | V <sub>vcc</sub> rising                                   |      |     | 4.3 | V     |  |

|                    | OVLO TITESTICIO                           | Hysteresis                                                |      | 150 |     | mV    |  |

|                    | DH UVLO Threshold                         | V <sub>BST</sub> to V <sub>SW</sub> Falling               |      | 2.0 |     | V     |  |

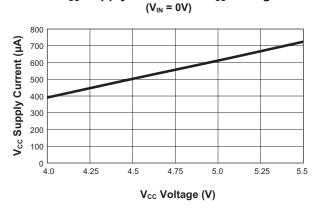

|                    |                                           | $V_{IN} = 0V$ ; $V_{CC} = 5V$                             |      | 600 |     |       |  |

|                    | Quiescent Current                         | $V_{IN} = 5V$ ; $V_{CC} = 5V$                             |      | 16  |     | μΑ    |  |

|                    |                                           | $V_{IN} = 0V$ to 5V, 100kHz; $V_{CC} = 5V$                |      | 350 |     |       |  |

|                    |                                           | EN = GND, BST Open                                        |      |     | 1.0 |       |  |

|                    | Shutdown Current                          | EN=GND, BST Connected to External Diode, Capacitor and SW |      | 25  | 50  | μΑ    |  |

|                    | DI DII Duive Resistance                   | Pull-Up                                                   |      | 3   |     | Ω     |  |

|                    | DL, DH Drive Resistance                   | Pull-Down                                                 |      | 1.7 |     | 72    |  |

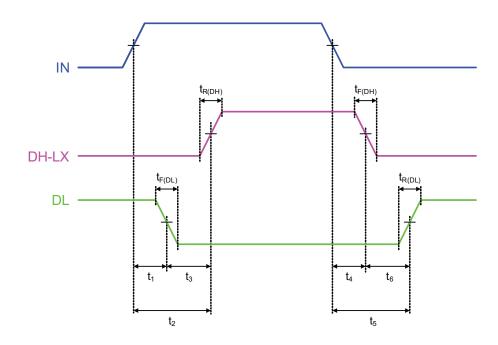

| t <sub>R(DL)</sub> | DL Rise Time                              | $C_{DL} = 0.5nF$                                          |      | 2   |     | ns    |  |

| $t_{R(DH)}$        | DH Rise Time                              | $C_{DH} = 0.5nF$                                          |      | 2   |     | ns    |  |

| $t_{F(DL)}$        | DL Fall Time                              | $C_{DL} = 0.5nF$                                          |      | 2   |     | ns    |  |

| $t_{F(DH)}$        | DH Fall Time                              | $C_{DH} = 0.5nF$                                          |      | 22  |     | ns    |  |

|                    | IN High to DH High Propagation Delay (t2) |                                                           |      | 130 |     | ns    |  |

|                    | IN-Low to DH-Low Propagation Delay (t4)   |                                                           |      | 35  |     | ns    |  |

|                    | IN-Low to DL-High Propagation Delay (t5)  |                                                           |      | 75  |     | ns    |  |

|                    | IN High to DL Low Propagation Delay (t1)  |                                                           |      | 65  |     | ns    |  |

|                    | DL-Low to (DH-LX)-High (t3)               |                                                           |      | 65  |     | ns    |  |

|                    | (DH-LX)-Low to DL-High (t6)               |                                                           |      | 40  |     | ns    |  |

|                    | SW Leakage Current                        | $V_{IN} = 5.5, V_{SW} = 0$                                |      |     | 1   | μΑ    |  |

|                    | EN Threshold Low                          |                                                           |      |     | 0.6 | V     |  |

|                    | EN Threshold High                         |                                                           | 1.4  |     |     | V     |  |

|                    | EN Leakage Current                        | $V_{IN} = 5.5V, V_{EN} = 0V$                              | -1.0 |     | 1.0 | μΑ    |  |

|                    | Over-Temperature Shutdown Threshold       |                                                           |      | 140 |     | °C    |  |

|                    | Over-Temperature Shutdown Hysteresis      |                                                           |      | 15  |     | °C    |  |

<sup>1.</sup> The AAT4910 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assured by design, characterization, and correlation with statistical process controls.

## 28V Half-Bridge Dual N-Channel MOSFET Driver

## **Timing Diagram**

### 28V Half-Bridge Dual N-Channel MOSFET Driver

### **Typical Characteristics**

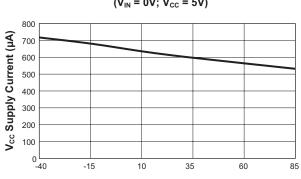

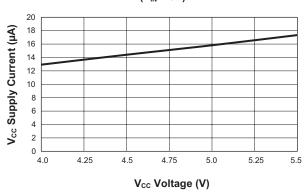

V<sub>cc</sub> Supply Current vs. V<sub>cc</sub> Voltage

V<sub>CC</sub> Supply Current vs. Temperature (V<sub>IN</sub> = 0V; V<sub>CC</sub> = 5V)

Temperature (°C)

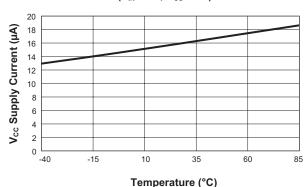

$V_{CC}$  Supply Current vs.  $V_{CC}$  Voltage  $(V_{IN} = 5V)$

$V_{CC}$  Supply Current vs. Temperature  $(V_{IN} = 5V; V_{CC} = 5V)$

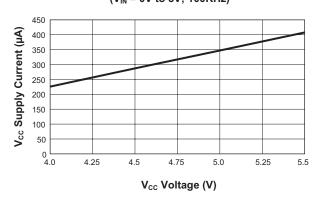

$\begin{array}{c} \textbf{V}_{\text{CC}} \ \textbf{Supply Current vs.} \ \textbf{V}_{\text{CC}} \ \textbf{Voltage} \\ (\textbf{V}_{\text{IN}} = \textbf{0V to 5V; 100KHz}) \end{array}$

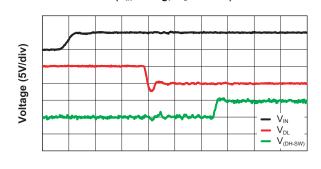

Propagation Delay and Break-Before-Make (V<sub>IN</sub> Rising; Q<sub>G</sub> = 5.6nC)

Time (20ns/div)

### 28V Half-Bridge Dual N-Channel MOSFET Driver

### **Typical Characteristics**

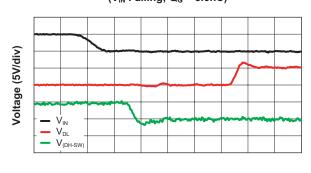

## Propagation Delay and Break-Before-Make (V<sub>IN</sub> Falling; Q<sub>G</sub> = 5.6nC)

Time (10ns/div)

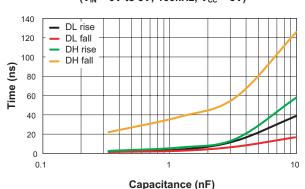

#### Rise and Fall Time vs. $C_{LOAD}$ ( $V_{IN} = 0V$ to 5V; 100kHz; $V_{CC} = 5V$ )

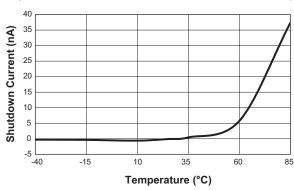

## Shutdown Current vs. Temperature $(V_{VCC} = V_{BST} = V_{IN} = 5V; V_{EN} = 0V; DH = DL = SW = Float)$

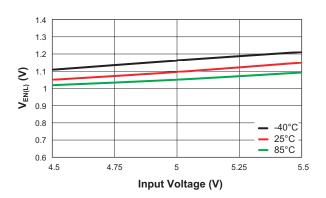

#### Input Low Threshold vs. Input Voltage

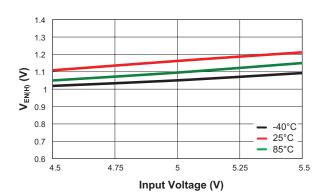

#### Input High Threshold vs. Input Voltage

### **Functional Block Diagram**

#### **Functional Description**

The AAT4910 is a dual MOSFET driver that takes a logic input (IN) and drives both high and low-side N-channel MOSFETs. It can be used to drive the power section of DC/DC converters, Class D audio power amplifiers, or other high-power devices requiring switched voltage. The device is powered from a 5V rail and includes circuitry to drive the high-side N-channel MOSFET with up to 28V power input. When driven low, the enable input (EN) turns off the driver and reduces the operating current to less than  $1\mu A$ . Over-temperature shutdown protects the AAT4910 in the case of a short circuit or defective MOSFET. High-side driver under-voltage lockout turns off the high-side MOSFET when there is insufficient voltage to drive the MOSFET preventing damage at startup or if the IN input is held high continuously.

#### High-Side/Low-Side MOSFET Driver

The AAT4910 turns on the high-side external MOSFET when IN is driven high, and turns on the low-side MOSFET when IN is driven low. The low  $3\Omega$  pull-up and  $1.7\Omega$  pull-down resistance allow fast turn-on and turn-off times and/or the capability to drive multiple large MOSFETs. The lower pull-down resistance ensures that the MOSFETs remain off during fast drain-voltage switching transients.

The high-side driver powers the gate of the external MOSFET to a voltage greater than the input, allowing it to fully turn on without a separate power supply rail. The high-side driver boost capacitor between SW and BST is charged when the low-side MOSFET is on via the 5V power source and the external rectifier. Once the capacitor is charged, the DH MOSFET gate driver output is powered from BST, allowing sufficient MOSFET gate voltage for full enhancement. An under-voltage lockout feature on the BST-to-SW voltage turns off the DH output if the voltage falls below the under-voltage threshold. This ensures that should the boost capacitor excessively discharge or is not able to fully charge, the MOSFET will not be driven to an intermediate state that would result in excessive power dissipation and could cause the MOSFET to fail.

High-to-low and low-to-high transitions include a break-before-make "dead" time when both MOSFETs are turned off. This insures that one MOSFET is fully turned off before the other MOSFET is turned on to prevent the possibility of shoot-through current.

Thermal overload protection turns off the AAT4910 should the die temperature exceed the 140°C threshold. This protects the AAT4910 from high ambient temperature conditions and MOSFET failures. At 15°C hysteresis prevents rapid cycling in and out of thermal shutdown.

#### **Application Information**

#### **Supply Capacitor**

The input capacitor provides a low impedance loop for the edges of pulsed current drawn by the AAT4910. A 4.7 $\mu$ F to 10 $\mu$ F X7R or X5R low ESR/ESL ceramic capacitor selected for the input is ideal for this function. To minimize tray resistance, the capacitor should be placed as closely as possible to the input pin in order to minimize EMI and input voltage ripple.

#### **Bootstrap Capacitor**

In order to fully turn on the high side external MOSFET while the low side MOSFET turns OFF, a bootstrap capacitor is connected between the BST pin and the SW pin. This capacitor is charged up to  $V_{\rm CC}$  through an external diode when the low side MOSFET is ON. The boost strap capacitor voltage rating should be able to withstand at least twice the maximum voltage supply, and its value should be at least fifteen times larger than the gate capacitor value. The bootstrap capacitance can be estimated by Equation 1:

**Eq. 1:**

$$C_{BST(MIN)} = 15 \cdot \frac{Q_{GATE}}{V_{CC} - V_{DIODE}}$$

For example, a Si4908DY dual N-channel MOSFET has a total gate charge of  $Q_{\text{GATE}}=$  6nC at  $V_{\text{GS}}=$  5V. Using  $V_{\text{CC}}=$  5V and  $V_{\text{DIODE}}=$  1V, then

$$C_{BST(MIN)} = 15 \cdot \frac{6nC}{5V - 1V} = 0.04 \mu F$$

A  $0.1\mu F/12V$  low ESR X7R ceramic capacitor is selected to handle twice the maximum supply voltage (5.5V) and to prevent voltage transient at the drain of the high side MOSFET.

#### **Shoot-Through Protection**

The high-side and low-side MOSFETs of the AAT4910 cannot conduct at the same time in order to prevent shoot-through current. When the clock pulse at IN pin rises, DL is first pulled down. The shoot-through protection circuit waits for about 60ns before pulling up DH. Similarly, when the clock pulse goes low, DH is pulled down first, and the circuit pulls up DL after about 40ns. In this way, the high-side and low-side MOSFETs are

never turned on at the same time to prevent the supply voltage shorts to ground. The time between the DH and DL pulses should be kept as short as possible to minimize current flows through the body diode of the low-side MOSFET(s). The break-before-make shoot-through protection significantly reduces the losses associated with the driver at high frequency.

#### **Output Inductor Selection**

A 2.2 $\mu$ H to 10 $\mu$ H inductor value with appropriate DCR is selected to maintain the peak inductor current below the maximum current of the high-side and low-side MOSFETs. The peak inductor current, which varies according to the driving frequency (PWM), should not exceed the inductor saturation current. In application where the driving frequency below 100KHz, a 4.7 $\mu$ H to 10 $\mu$ H inductor should be used to avoid the peak inductor current exceeding the maximum current of the MOSFETs.

#### **Thermal Calculations**

The power dissipation of the AAT4910 MOSFETs driver includes power dissipation in the MOSFETs due to charging and discharging the gate capacitance, quiescent current power dissipation, and transient power in the driver during output transitions (the transient power is usually very small and losses in it can be neglected). The maximum package power dissipation can be estimated by Equation 2:

Eq. 2:

$$\begin{aligned} \textbf{Eq. 2:} \ & P_{D(MAX)} = V_{CC} \cdot I_{IN} = \ \frac{T_{J(MAX)} - T_A}{\theta_{JA}} \\ & = I_Q \cdot V_{CC} + Q_{G(HS)} F_{SW} \cdot V_{CC} + Q_{G(LS)} F_{SW} \cdot V_{CC} \end{aligned}$$

Where:

$T_{J(MAX)}$  is the junction temperature of the dice (C°).

$T_{AMB}$  is the ambient temperature (C°).

$\theta_{JA}$  =160 °C/W is the thermal resistance (C°/W).

$I_0$  is the operating current of the driver (mA).

$Q_{\text{G(HS)}}$  and  $Q_{\text{G(LS)}}$  are the gate charge of high side and low side MOSFET (nC).

$F_{SW}$  is the switching frequency (MHz).

The maximum junction temperature can be derived from Equation 2 for the SC70JW-8 package:

**Eq. 3:**

$$T_{J(MAX)} = P_{D(MAX)} \cdot \theta_{JA} + T_{AMB}$$

9

For example, consider the AAT4910 drives the Si4908DY dual N-channel MOSFET whose maximum gate charge specified as 6nC for  $V_{\rm GS}=5V$ . The total power dissipation in the driver at a switching frequency of 100kHz equals:

$$P_{TOTAL} = 5V \cdot 450 \mu A + 2(5V \cdot 6nC \cdot 100 kHz) = 8.25 mW$$

The maximum junction temperature at 100kHz is determined by Equation 3:

$$T_{J(MAX)} = 8.25 \text{mW} \cdot 160 \text{ °C/W} + 85 \text{ °C} = 86.3 \text{°C}$$

This is well within the thermal limits for safe operation of the device.

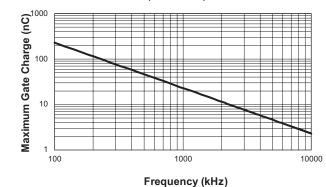

#### **Gate Drive Current Ratings**

Assuming the maximum gate charge of high side and low side MOSFET are equal to each other, the maximum gate drive capability for the designed maximum junction temperature without an external resistor can be derived from Equation 2:

**Eq. 4:**

$$Q_{G(MAX)} = \frac{1}{2 \cdot F_{SW}} \left( \frac{T_{J(MAX)} - T_{AMB}}{\theta_{JA} \cdot V_{IN}} - I_{Q} \right)$$

The relationship between gate capacitance, turn-on/turn-off time, and the MOSFET driver current rating can be determined by Equation 5:

Eq. 5:

$$I_{G(MAX)} = C_{G(MAX)} \cdot \frac{dV}{dt}$$

Where:

$I_{\text{G(MAX)}}$  is the peak drive current for a given apply voltage  $C_{\text{G(MAX)}}$  is the maximum gate capacitance dV is gate-to-source voltage of the MOSFET dt is rising time of the MOSFET gate voltage

The relationship between  $C_{G(MAX)}$ ,  $Q_{G(MAX)}$ , and  $V_{GS}$  is given by Equation 6:

Eq. 6:

$$C_{G(MAX)} = \frac{Q_{G(MAX)}}{V_{GS}}$$

The peak current drive requirements for a given MOSFET gate voltage can be derived from Equations 5 and 6:

Eq. 7:

$$I_{G(MAX)} = \frac{Q_{G(MAX)}}{dt}$$

#### **Design Example**

$$V_{IN} = 5V$$

$V_{GS} = 5V$

$F_{SW} = 500 \text{ kHz}$

$\theta_{1A} = 160^{\circ}\text{C/W}$

$$I_Q = 8mA$$

$$T_{J(MAX)} = 120$$

°C

$T_{AMB} = 85$ °C

$$t_{RISE} = dt = 60ns$$

$$Q_{G(MAX)} = \frac{1}{2 \cdot 500 \text{KHz}} \left( \frac{120^{\circ}\text{C} - 85^{\circ}\text{C}}{160^{\circ}\text{C/W} \cdot 5\text{V}} - 8\text{mA} \right) = 36\text{nC}$$

$$C_{\text{G(MAX)}} = \frac{Q_{\text{G(MAX)}}}{V_{\text{GATE}}} = \frac{36nC}{5V} = 7nF$$

$$I_{G(MAX)} = \frac{Q_{G(MAX)}}{dt} = \frac{36nC}{60ns} = 0.6A$$

Figure 1 shows that the maximum gate drive capability of the MOSFET driver will derate when the switching frequency increases.

## Maximum Gate Charge vs. Frequency @ 25°C (T<sub>J</sub> = 120°C)

Figure 1: Maximum Gate Charge vs. Switching Frequency.

### 28V Half-Bridge Dual N-Channel MOSFET Driver

#### **Typical Applications**

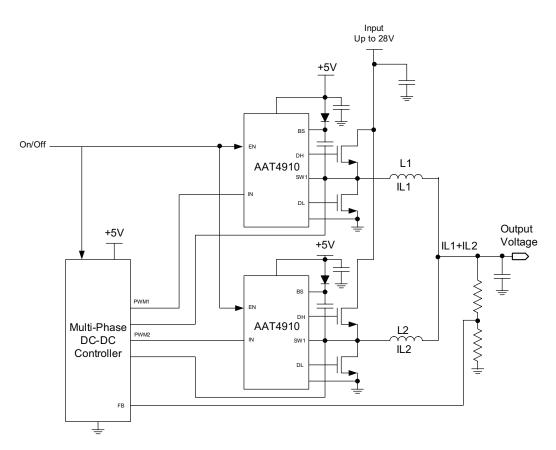

#### **Multi-Phase Synchronous Buck Converter**

The most common AAT4910 applications include multiphase DC/DC converter output power stages, DC motor drive, and Class D audio power amplifier. Figure 2 shows a typical configuration when used as a 2-phase buck converter power stage with synchronous rectification. The EN pin can be used to force the LX output to a high impedance state which enables the output inductor to

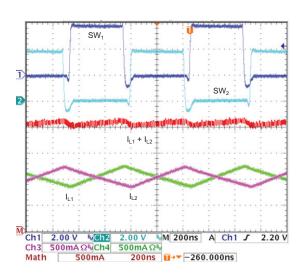

operate in discontinuous conduction mode (DCM) in order to improve the efficiency under light load conditions. The body diode associated with the low side switching MOSFET gives the AAT4910 inductive switching capability, and clamps the LX node at one diode drop below GND during the break-before-make time. The multiphase buck converter assures a stable and high performance topology for high currents and low voltages which are demanded in desktop computers, workstations, and servers. Figure 3 shows an output ripple current reduction due to 2-phase cancellation.

Figure 2: AAT4910 2-Phase Synchronous Buck Converter Power Stage.

Figure 3: Output Current Ripple Reduction  $(I_{L1} + I_{L2})$  due to 2-Phase Cancellation.

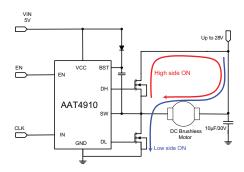

#### **Motor Drive**

The AAT4910 is also ideally suited for use as an efficient output driver for DC brushless motor control. The inductive load switching capability of the AAT4910 eliminates the need for external diodes. A typical half-bridge motor control circuit is illustrated in Figure 4. In half-bridge motor control, one end of the motor is connected to the SW node of the driver, and the other end is connected to the power supply or ground. The speed of the motor is controlled by the PWM duty cycle at the IN terminal of the AAT4910. When the high-side MOSFET turns OFF and the low-side MOSFET turns ON, the current flows through the motor to ground from the supply voltage (blue arrow). During the ON time, the low-side MOSFET turns OFF and the high-side MOSFET turns ON. The winding current keeps the induced current flowing in the same direction but exponentially decays toward zero.

Figure 4: Half-Bridge Motor Drive Using AAT4910 MOSFET Driver.

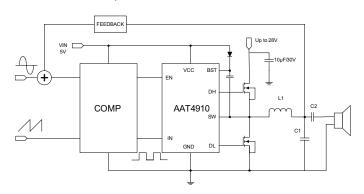

#### **Class D Audio Amplifier**

The AAT4910 is also ideally suited for use as an efficient output driver for a Class D audio amplifier. In this type of amplifier, the switches are either fully on or fully off, significantly reducing conduction losses in the output power devices. In this way, Class D audio offers a superior efficiency over 90%, which can not be achieved with traditional Class AB audio. A typical Class D audio amplifier block diagram is illustrated in Figure 5, in which the audio signal is modulated by the PWM carrier signal which drives the IN terminal of the AAT4910. A low pass filter (L1, C1) at the last stage removes the high frequency of the PWM carrier signal. Typically, a  $1000\mu F$  DC blocking capacitor (C2) is used at the output to provide DC short circuit protection.

Figure 5: Typical Class D Audio Amplifier Block Diagram.

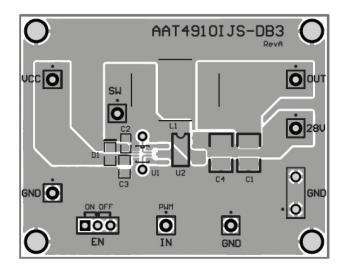

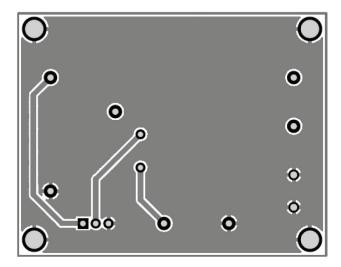

#### Layout

The suggested PCB layout for the AAT4910 is shown in Figures 7 and 8. The following guidelines should be used to help ensure a proper layout.

- 1. Place the driver as close as possible to the MOSFETs.

- 2. Place the decoupling capacitor C3 as close as possible to the VCC and GND pins.

- DH, LX, DL, and GND should connect as closely as possible to the MOSFETs to minimize propagation delay.

- The high-current loop between the high-side and low-side MOSFETs and the input capacitor should be kept as small as possible.

- 5. The trace connected to the drain and source MOSFETs should be large to improve heat dissipation.

Figure 6: AAT4910 Evaluation Board Schematic.

Figure 7: AAT4910 Evaluation Board Top Side Layout.

Figure 8: AAT4910 Evaluation Board Bottom Side Layout.

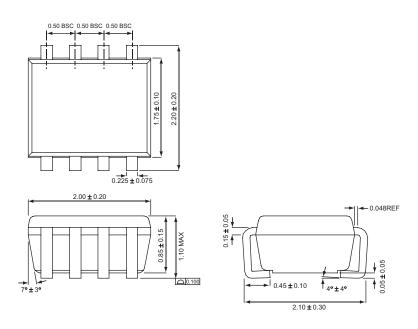

#### **Ordering Information**

| Package  | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|----------|----------------------|------------------------------------------|

| SC70JW-8 | 5HXXY                | AAT4910IJS-T1                            |

Skyworks Green<sup>TM</sup> products are compliant with all applicable legislation and are halogen-free. For additional information, refer to *Skyworks Definition of Green*<sup>TM</sup>, document number S004-0074.

#### **Package Information**

#### **SC70JW-8**

All dimensions in millimeters.

- 1. XYY = assembly and date code.

- 2. Sample stock is generally held on part numbers listed in BOLD.

Copyright © 2012 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.

Skyworks, the Skyworks symbol, and "Breakthrough Simplicity" are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.